Amazing Info About What Is A Netlist In VLSI

Unveiling the Mysteries of the Netlist in VLSI

1. What Exactly is a Netlist? Think of it as a Recipe for Circuits!

Ever wonder how those incredibly complex computer chips get made? It's not magic, but it is pretty darn clever engineering. One crucial ingredient in the process is the netlist. Simply put, a netlist in the context of Very-Large-Scale Integration (VLSI) is a text-based description detailing the connectivity of an electronic circuit. Its like a blueprint, a recipe, or even a wiring diagram, but instead of wires and components drawn on paper, it uses a specific language to define how all the different parts connect to each other. Imagine Legos, but for circuits the netlist tells you exactly how to snap them together.

Think of it like this: you have a box of electronic components transistors, resistors, capacitors, and more. The netlist acts as the instruction manual, guiding the software on how to wire these components together to create the desired functionality, whether it's a blazingly fast processor or the memory in your phone. Without a netlist, the manufacturing process would be like trying to build a house without architectural plans — chaotic, and probably not very successful! Its the foundation upon which all subsequent steps in VLSI design are built.

The netlist itself isn't a visual representation of the circuit. It's more of a list (hence the name!) of connections. Each line in the netlist typically describes one connection, specifying the components involved and the pins or terminals that are linked. This seemingly simple list is the key to translating the abstract design into a physical reality.

Its written in a Hardware Description Language (HDL) like Verilog or VHDL, using special keywords to identify components, pins, and nets (the conductive paths connecting the pins). A well-structured netlist is essential for simulation, verification, and ultimately, the physical implementation of the circuit on a silicon chip. It's the common language between the design engineers and the manufacturing tools.

Delving Deeper

2. Anatomy of a Netlist

While the specific syntax can vary depending on the HDL used (Verilog, VHDL, etc.), a typical netlist includes several key elements. First, there's the component declaration, which identifies each individual component used in the circuit, specifying its type (e.g., a transistor, a resistor) and its unique name within the design. Next, there's the instance declaration, which creates an instance of a pre-defined component or module.

Then comes the crucial part: the net declarations. Nets are the wires that connect the various components together. Each net declaration specifies which components are connected to that particular net. This is where the precise connectivity of the circuit is defined. Finally, the netlist may also include other information, such as power and ground connections, clock signals, and test points.

Imagine a simple circuit with a transistor and a resistor. The netlist would define the transistor's connections (gate, source, drain) and the resistor's connections (terminal 1, terminal 2). It would then specify which terminals are connected to which nets, creating the electrical pathways for the circuit to function. You might see lines that look something like "connect transistor.drain to resistor.terminal1" - albeit in a much more formal syntax, of course.

The beauty of a netlist is its abstraction. It doesnt care about the physical layout of the components on the chip. It only cares about the logical connectivity. This allows designers to focus on the functionality of the circuit without getting bogged down in the details of physical implementation. The physical layout is handled later by place and route tools, which take the netlist as input and determine the optimal placement of components and routing of wires on the chip.

What Is Netlist? YouTube

Why is the Netlist So Darn Important?

3. Netlist's Key Role in VLSI Design

The netlist isn't just some technical document; it's absolutely vital to the entire VLSI design flow. Think of it as the linchpin holding everything together. One of its primary roles is in simulation. Before a chip is actually fabricated, it needs to be thoroughly simulated to ensure that it behaves as expected. Simulators use the netlist to create a virtual model of the circuit, allowing engineers to test its functionality under various conditions.

The netlist also plays a crucial role in verification. Verification tools use the netlist to check that the circuit meets certain design rules and specifications. This helps to catch errors early in the design process, before they can lead to costly fabrication mistakes. For example, verification tools can check for timing violations, signal integrity issues, and power consumption problems.

Furthermore, the netlist is the foundation for physical implementation. Place and route tools, which are responsible for physically laying out the components and routing the wires on the chip, take the netlist as their starting point. These tools use sophisticated algorithms to optimize the layout for performance, power consumption, and area. Without an accurate and complete netlist, the place and route tools would be unable to create a functional chip layout.

Finally, the netlist serves as a common language for all the different tools and engineers involved in the VLSI design process. It allows designers to communicate their ideas clearly and unambiguously, and it ensures that all the tools are working from the same understanding of the circuit. In short, the netlist is the glue that holds the entire VLSI design process together.

Netlist File In Digital VLSI Design Flow Bale Tulu Kalpuga

From Netlist to Silicon

4. The Netlist's Path Through VLSI Flow

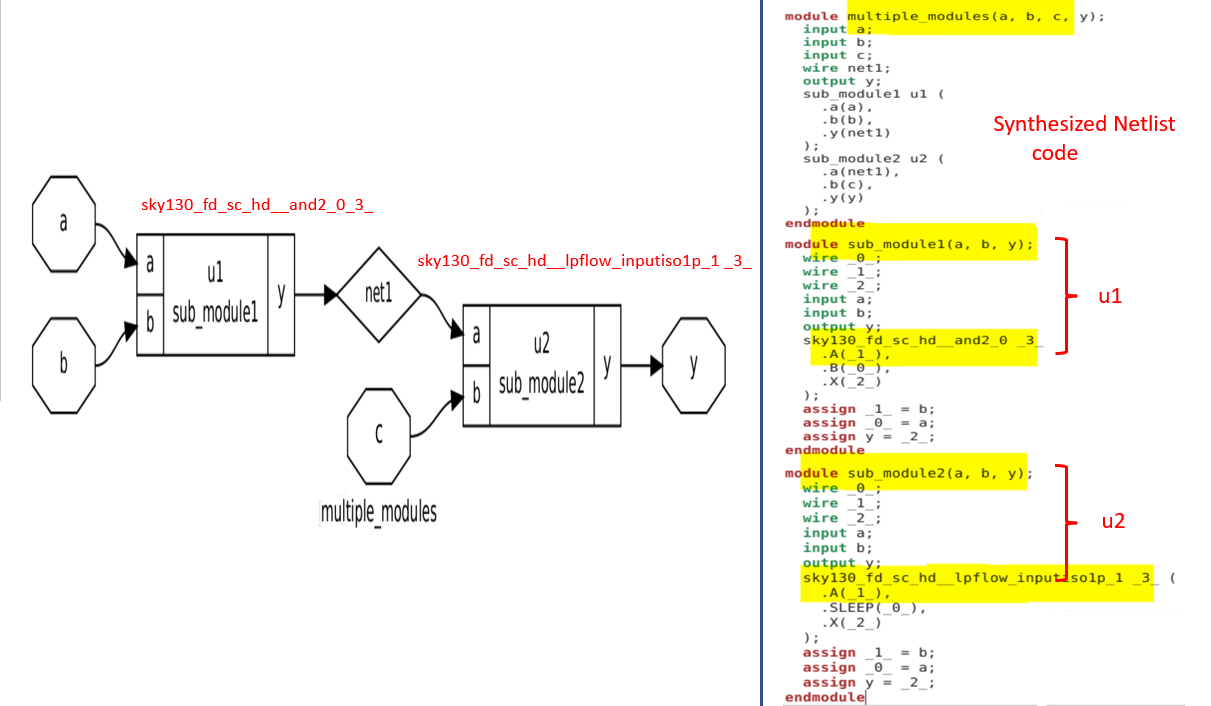

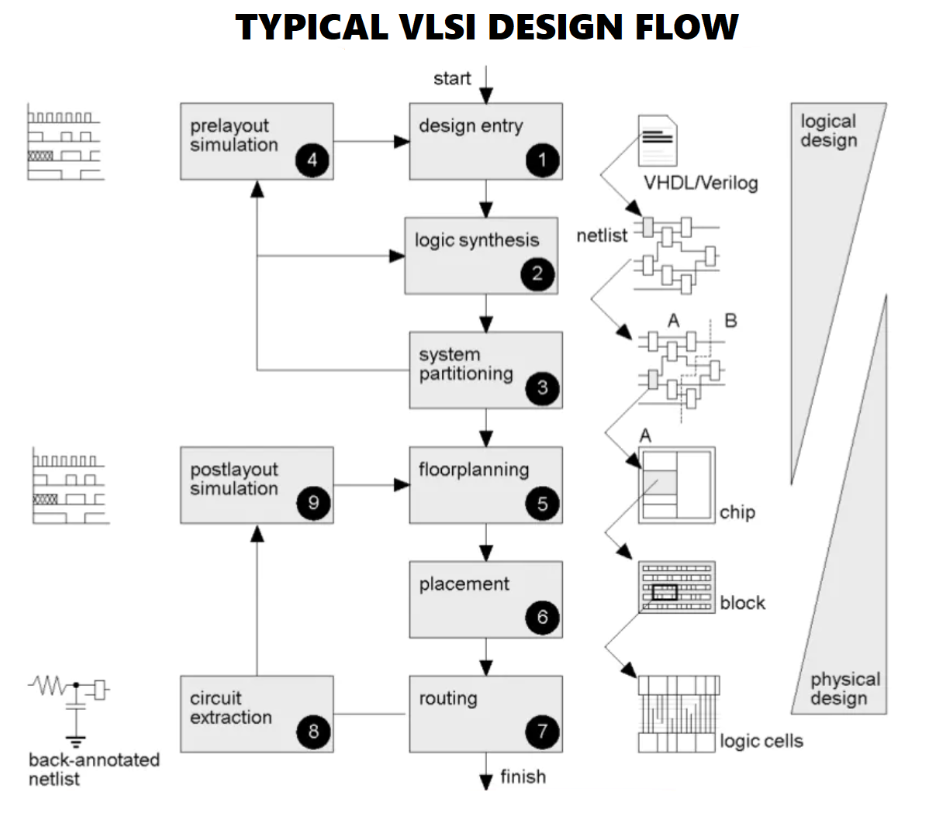

The netlist's journey doesn't end after its creation; it's just the beginning. Once the design is captured in a netlist, several tools are used to verify, synthesize, and eventually convert it into a physical layout. The first step is often logic synthesis. This process transforms the high-level description in the netlist into a gate-level representation, using standard logic gates like AND, OR, and NOT gates. This gate-level netlist is then optimized for performance, area, and power consumption.

Next, timing analysis is performed to ensure that the circuit meets its timing specifications. This involves analyzing the delays through the various paths in the circuit and identifying any potential timing violations. If violations are found, the design may need to be modified to improve its timing performance.

The next stage is place and route, where the logic gates are physically placed on the chip and the interconnections between them are routed. This is a complex optimization problem, as the placement and routing can significantly impact the circuit's performance, power consumption, and area. The place and route tools use the netlist as a guide to ensure that all the connections are made correctly.

Finally, the physical layout is verified to ensure that it meets all the design rules and specifications. This includes checking for shorts, opens, and other physical defects. Once the layout is verified, it can be used to create the masks for fabricating the chip. It's a long and complex process, but it all starts with that humble netlist.

Solved TYPICAL VLSI DESIGN FLOW Start Netlist Finish

Netlist Formats

5. A Glimpse into the Various Netlist Languages

While the core concept of a netlist remains the same, there are different formats in which it can be represented. SPICE (Simulation Program with Integrated Circuit Emphasis) is one of the oldest and most widely used formats, particularly for analog circuit simulation. It uses a specific syntax to describe the components and connections in a circuit, and it's well-suited for detailed circuit analysis. It's the granddaddy of netlist formats, and still kicking!

Verilog and VHDL (VHSIC Hardware Description Language) are more modern HDLs commonly used for digital circuit design. They provide a more abstract way to describe the circuit's behavior, allowing designers to focus on the functionality rather than the specific implementation details. Verilog and VHDL netlists are often used as input to synthesis tools, which automatically generate a gate-level implementation of the circuit.

Other netlist formats exist, often tailored to specific tools or applications. The choice of netlist format depends on the design methodology, the type of circuit being designed, and the tools being used. It's like choosing the right cooking language based on whether youre baking a cake (SPICE for detailed ingredient analysis) or writing a cookbook (Verilog/VHDL for general recipes).

Ultimately, the key is to choose a format that is well-suited to the task at hand and that is supported by the tools being used. Regardless of the format, the netlist remains the essential link between the design and the physical implementation of the circuit.

What Is Netlist? Siliconvlsi

FAQ About Netlists in VLSI

6. Your Burning Questions Answered!

Let's address some common questions that might be lingering in your mind:

7. What happens if there's an error in the netlist?

A mistake in the netlist can have serious consequences! It can lead to a circuit that doesn't function correctly, doesn't meet its performance specifications, or even damages the chip during fabrication. Thats why thorough verification is so critical.

8. Can I edit a netlist directly?

Technically, yes, you can edit a netlist directly. But it's generally not recommended, especially for complex designs. It's very easy to introduce errors that are difficult to track down. It's usually better to modify the design at a higher level of abstraction and then regenerate the netlist.

9. Is a netlist the same as a schematic?

Not quite. A schematic is a graphical representation of a circuit, while a netlist is a text-based description. A schematic is great for understanding the overall structure of the circuit, while a netlist is more precise and is used by automated tools. They complement each other in the design process. The schematic gives you the picture, while the netlist gives you the instructions.